Analog Multiplier

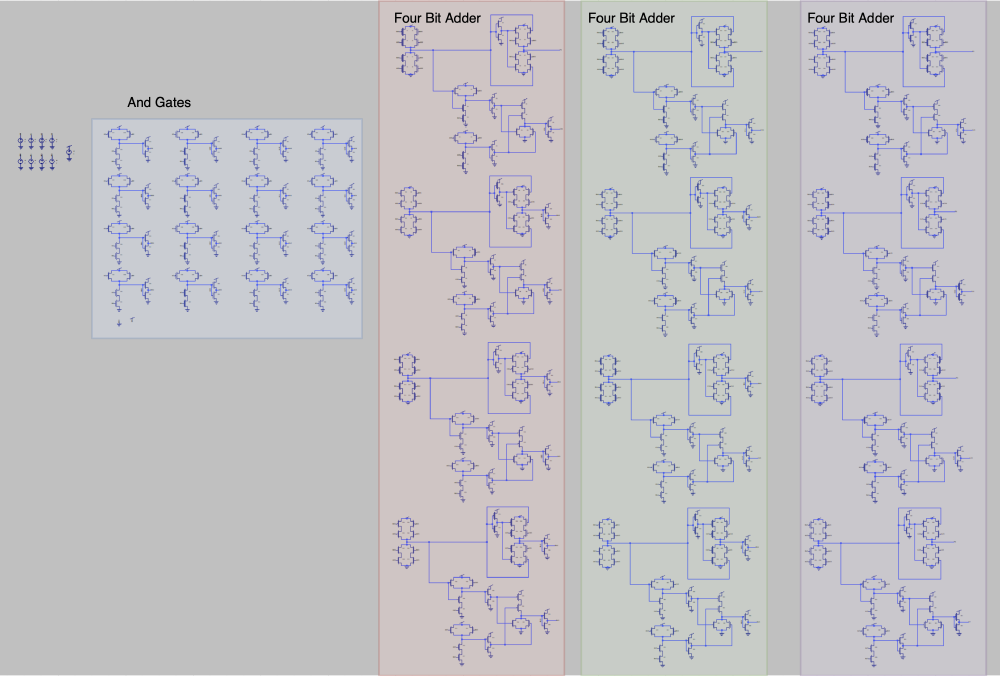

I designed and implemented a 4-bit multiplier using CMOS transistors in LTSpice. As a part of this project, tests for different logic gates and the multiplicities of the nMOS and pMOS transistors were optimized to ensure that the gates were outputting strong logical highs and lows.

These logic gates were used to construct a 1-bit full adder, a 4-bit full adder, and then a 4-bit multiplier. The voltage transfer characteristics and propogation delays at each step were calculated to estimate the fastest clock speed possible for the system. This was shown visually by seeing how long it tok the final output bit of the multiplier to turn. (Full Paper)